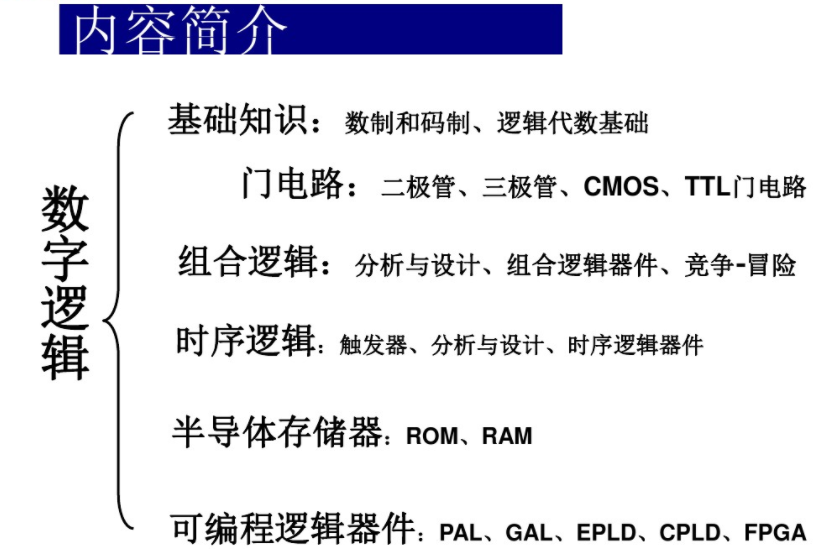

- 1.0 邏輯代數(shù)內(nèi)容簡(jiǎn)介

- 1.1 模擬信號(hào)與數(shù)字信號(hào)

- 1.2 數(shù)制與碼制

- 1.3 基本邏輯運(yùn)算

- 1.4 組合邏輯運(yùn)算

- 1.5 邏輯運(yùn)算規(guī)律

- 2.1 邏輯代數(shù)規(guī)則

- 2.2 邏輯函數(shù)的表示方法

- 2.3 最小項(xiàng)與最大項(xiàng)

- 2.4 邏輯表達(dá)式的化簡(jiǎn)

- 2.5 變量卡諾圖

- 2.6 函數(shù)卡諾圖

- 2.7 函數(shù)卡諾圖化簡(jiǎn)方法

- 2.8 具有約束的卡諾圖化簡(jiǎn)

- 3.0 集成門電路內(nèi)容簡(jiǎn)介

- 3.1 集成電路

- 3.2 簡(jiǎn)單門電路1

- 3.3 簡(jiǎn)單門電路2

- 3.4 TTL門電路

- 3.5 TTL門電路輸出特性

- 3.6 TTL門電路電壓傳輸特性與噪聲容限

- 3.7 TTL門電路輸入特性與扇出系數(shù)

- 3.8 TTL門電路輸入端負(fù)載特性

- 3.9 TTL門電路靜態(tài)功耗與延遲時(shí)間

- 3.10 集電極開路門

- 3.11 三態(tài)門

- 3.12 CMOS門

- 3.13 CMOS傳輸門

- 4.0 組合數(shù)字電路內(nèi)容簡(jiǎn)介

- 4.1 組合數(shù)字電路分析

- 4.2.1 組合數(shù)字電路設(shè)計(jì)

- 4.2.2 基本邏輯關(guān)系的Verilog HDL實(shí)現(xiàn)

- 4.3.1 加法器

- 4.3.2 半加器和全加器的Verilog HDL實(shí)現(xiàn)

- 5.1.1 編碼器

- 5.1.2 編碼器的Verilog HDL實(shí)現(xiàn)

- 5.1.3 編碼器74LS148的Multisim仿真

- 5.2.1 二進(jìn)制譯碼器

- 5.2.2 138譯碼器的Verilog HDL實(shí)現(xiàn)

- 5.2.3 138譯碼器的Multisim仿真

- 5.3 代碼轉(zhuǎn)換譯碼器

- 5.4.1 顯示譯碼器

- 5.4.2 顯示譯碼器的Verilog HDL實(shí)現(xiàn)

- 5.4.3 顯示譯碼器74LS47的實(shí)驗(yàn)

- 6.1.1 數(shù)據(jù)選擇器

- 6.1.2 數(shù)據(jù)選擇器的Verilog HDL實(shí)現(xiàn)

- 6.1.3 數(shù)據(jù)選擇器的Multisim功能驗(yàn)證仿真

- 6.2.1 數(shù)碼比較器

- 6.2.2 數(shù)碼比較器的Verilog HDL實(shí)現(xiàn)

- 6.3 競(jìng)爭(zhēng)與冒險(xiǎn)

- 7.1 基本R-S觸發(fā)器

- 7.2 同步R-S觸發(fā)器

- 7.3 D型觸發(fā)器

- 7.4 J-K觸發(fā)器

- 7.5 邊沿觸發(fā)器

- 7.6 鎖存器

- 7.7 觸發(fā)器的Multisim仿真實(shí)驗(yàn)

- 8.1 時(shí)序電路的特點(diǎn)與分類

- 8.2 同步時(shí)序電路的分析

- 8.3 異步時(shí)序電路的分析

- 8.4 同步時(shí)序電路的設(shè)計(jì)1

- 8.5 同步時(shí)序電路的設(shè)計(jì)2

- 8.6 有限狀態(tài)機(jī)的Verilog HDL實(shí)現(xiàn)

- 8.7 狀態(tài)機(jī)實(shí)現(xiàn)交通燈控制的實(shí)驗(yàn)

- 9.1.1 中規(guī)模同步加法計(jì)數(shù)器

- 9.1.2 計(jì)數(shù)器160的Verilog HDL實(shí)現(xiàn)

- 9.1.3 計(jì)數(shù)器74LS160的實(shí)驗(yàn)

- 9.2.1 同步加法計(jì)數(shù)器的應(yīng)用

- 9.2.2 同步計(jì)數(shù)器74LS160構(gòu)成百進(jìn)制計(jì)數(shù)器Multisim仿真

- 9.2.3 計(jì)數(shù)器實(shí)現(xiàn)60秒計(jì)數(shù)的實(shí)驗(yàn)

- 9.3.1 中規(guī)模同步可逆計(jì)數(shù)器

- 9.3.2 計(jì)數(shù)器192的Verilog HDL實(shí)現(xiàn)

- 9.4.1 中規(guī)模異步加法計(jì)數(shù)器

- 9.4.2 計(jì)數(shù)器90-93的Verilog HDL實(shí)現(xiàn)

- 9.4.3 異步計(jì)數(shù)器74LS90的Multisim功能驗(yàn)證仿真

- 9.5 異步加法計(jì)數(shù)器的應(yīng)用

- 9.6.1 寄存器

- 9.6.2 D觸發(fā)器構(gòu)成的移位寄存器型計(jì)數(shù)器的Multisim仿真

- 9.7.1 環(huán)形計(jì)數(shù)器

- 9.7.2 扭環(huán)形計(jì)數(shù)器

- 9.7.3 扭環(huán)形計(jì)數(shù)器的Verilog HDL實(shí)現(xiàn)

- 9.8 順序脈沖發(fā)生器

- 9.9 序列脈沖發(fā)生器

- 10.1 只讀存儲(chǔ)器ROM

- 10.2 ROM的應(yīng)用

- 10.3 隨機(jī)存儲(chǔ)器RAM

- 10.4.1 可編程邏輯器件概述

- 10.4.2 通用陣列邏輯GAL

- 10.4.3 CPLD與FPGA

- 11.1 施密特觸發(fā)器

- 11.2 單穩(wěn)態(tài)觸發(fā)器

- 11.3 多諧振蕩器

- 11.4.1 555定時(shí)器

- 11.4.2 555定時(shí)器的應(yīng)用1

- 11.4.3 555定時(shí)器的應(yīng)用2

- 11.4.4 555定時(shí)器的應(yīng)用3

- 11.4.5 555定時(shí)器應(yīng)用電路的Multisim仿真

- 12.1.1 數(shù)-模轉(zhuǎn)換器DAC

- 12.1.2 數(shù)-模轉(zhuǎn)換器DAC的技術(shù)指標(biāo)

- 12.2.1 模-數(shù)轉(zhuǎn)換器ADC

- 12.2.2 并行比較型ADC

- 12.2.3 逐次逼近型ADC

- 12.2.4 雙積分型ADC

- 12.2.5 模-數(shù)轉(zhuǎn)換器的技術(shù)指標(biāo)

- 12.3 AD與DA的Multisim仿真

課前預(yù)習(xí),課堂理解,課后練習(xí),溫故知新把握重點(diǎn),突破難點(diǎn),注重特點(diǎn),融會(huì)貫通重視實(shí)踐,勤思多練,善于歸納,勇于創(chuàng)新(1)邏輯代數(shù)是分析和設(shè)計(jì)數(shù)字電路的重要工具,應(yīng)熟練掌握。

(2)重點(diǎn)掌握各種常用數(shù)字邏輯電路的邏輯功能、外部特性及典型應(yīng)用。對(duì)其內(nèi)部電路結(jié)構(gòu)和工作原理不必過于深究。

(3)掌握基本的分析和設(shè)計(jì)方法。

(4)本課程實(shí)踐性很強(qiáng)。應(yīng)重視習(xí)題、基礎(chǔ)實(shí)驗(yàn)和綜合實(shí)訓(xùn)等實(shí)踐性環(huán)節(jié)。

(5)此外,注意培養(yǎng)和提高查閱有關(guān)技術(shù)資料和數(shù)字集成電路產(chǎn)品手冊(cè)的能力。

課程目錄:

第一章數(shù)制與編碼

內(nèi)容提要:

(1)模擬信號(hào)、數(shù)字信號(hào)及其之間的區(qū)別,以及數(shù)字電路的特點(diǎn)。

(2)進(jìn)位計(jì)數(shù)規(guī)則和各種不同數(shù)制之間的轉(zhuǎn)換方法。

(3)二進(jìn)計(jì)數(shù)制的基本特點(diǎn)及其在計(jì)算機(jī)中的表示形式。

(4)加權(quán)碼、非加權(quán)碼及字符代碼

1.1.2數(shù)字電路的特點(diǎn)

·數(shù)字電路的結(jié)構(gòu)是以二值數(shù)字邏輯為基礎(chǔ)的,其中的工作信號(hào)是離散的數(shù)字信號(hào)。電路中的電子器件工作于開關(guān)狀態(tài)。

·數(shù)字電路分析的重點(diǎn)已不是其輸入、輸出間波形的數(shù)值關(guān)系,而是輸入、輸出序列間的邏輯關(guān)系。

·所采用的分析工具是邏輯代數(shù),表達(dá)電路的功能主要是功能表、真值表、邏輯表達(dá)式、布爾函數(shù)以及波形圖。

·數(shù)字系統(tǒng)一般容易設(shè)計(jì)。

·信息的處理、存儲(chǔ)和傳輸能力更強(qiáng)。

·數(shù)字系統(tǒng)的精確度及精度容易保存一致。

·數(shù)字電路抗干擾能力強(qiáng)。

·數(shù)字電路容易制造在IC芯片上。